如何在PYNQ中创建FIR滤波器并与之交互

FPGA设计的关键要素之一是数字滤波器的实现,事实上,去年我们研究了如何使用带有Zmods的eclipse Z7板来实现数字滤波器。

但是,该项目需要使用信号发生器等形式的外部硬件。我认为创建一个使用PYNQ的示例可能是一个好主意,它使我们能够使用Python生成任意信号,过滤它并绘制结果波形。

在使用PYNQ的项目中,我们将能够可视化输入和输出波形。

Vivado设计

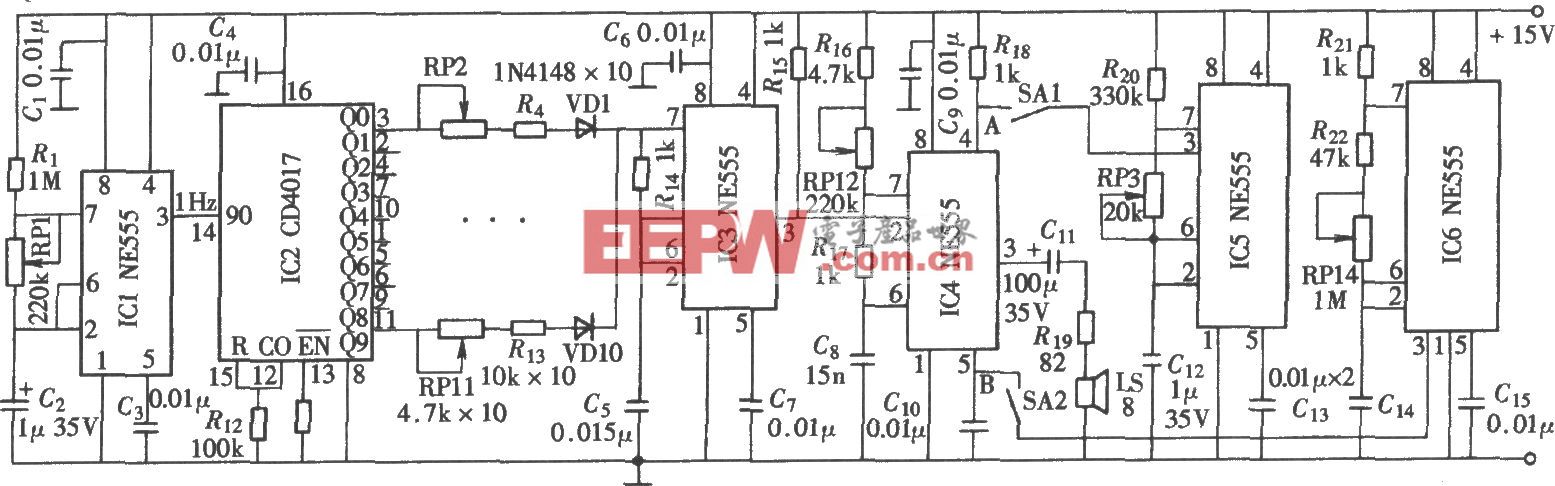

为了开始这个项目,我们将在Vivado实现一个设计。本设计将FIR编译器连接到可编程逻辑中的DMA。这将允许我们通过FIR滤波器传输大量的样本。

为此,我们需要以下IP块

•Zynq ultrascale + MPSOC处理系统

•中断控制器

•AXI直接存储器存取

•冷杉编译器

•智能互联

•AXI互连

•处理器复位系统

•Concat块

这些块需要按如下方式配置

Zynq UltraScale+ MPSoC处理系统-为Avnet ZU板配置,在此IP块上,我还启用了saxi HPC连接,以及PL PS IRQ

对于FIR编译器,我将实现一个简单的低通滤波器,采样率为100 Msps,时钟速率为100MHz。这意味着我们将能够处理高达50兆赫的信号。

为了设计滤波器,我再次使用TFilter设计低通滤波器,通带定义为0-25MHz,阻带定义为30MHz以上。

生成的系数可以复制到FIR编译器中

由于我们正在使用16位输入,输出将增长到33位,然而,为了确保DMA更容易工作,我们将截断结果为32位。

如果我们愿意,我们可以修改设计,使过滤器系数能够在飞行中上传。

由于我们正在使用DMA,我们需要确保FIR编译器AXI流接口具有正确的信号数量。我们特别需要DMA的TLast信号。

当涉及到DMA时,我们需要配置它以支持最多26位的缓冲区长度寄存器。同时确保读通道是16位,写通道是32位。

完成的解决方案应该如下图所示(TCL脚本附属于下面的项目)

图完成后,我们可以构建获得硬件切换(HWH)文件和位流的项目。

PYNQ

要开始创建笔记本,我们首先需要获取ZU板的PYNQ映像(在这里可用),并将ISO映像写入SD卡。一旦SD卡准备好了,我们就可以启动主板了。

通过将ZU板连接到以太网,我们可以将该板映射为网络位置,并将生成的HWH和位文件传输到ZU板。

确保使用不同的凭据检查连接,密码是xilinx, xilinx。

确保当您上传比特和HWH时,它们的名称相同。

笔记本创造

为了开始创建笔记本,我们将完全在python中执行过滤。

这将显示下面的信号

如果我们对这个信号做FFT

我们可以在FFT中看到信号的频率

为了在硬件上执行过滤,我们可以使用下面的代码,而不是这个信号应该通过过滤器。

我们将使用pynq allocate来定义发送和接收缓冲区所需的连续内存分配。我们将使用上面生成的相同信号

绘制FFT也给出

现在让我们生成一个应该被过滤掉的信号

如果我们要运行过滤器

运行硬件示例提供

总结

本项目展示了如何使用PYNQ轻松学习FIR滤波器,我们可以使用PYNQ环境创建简单的信号处理演示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码