正交解码及在旋转编码器中的应用

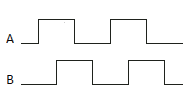

正交解码

module quad(clk, quadA, quadB, count); input clk, quadA, quadB; output [7:0] count; reg quadA_delayed, quadB_delayed; always @(posedge clk) quadA_delayed <= quadA; always @(posedge clk) quadB_delayed <= quadB; wire count_enable = quadA ^ quadA_delayed ^ quadB ^ quadB_delayed; wire count_direction = quadA ^ quadB_delayed; reg [7:0] count; always @(posedge clk)begin if(count_enable) begin if(count_direction) count<=count+1; else count<=count-1; end end endmodule

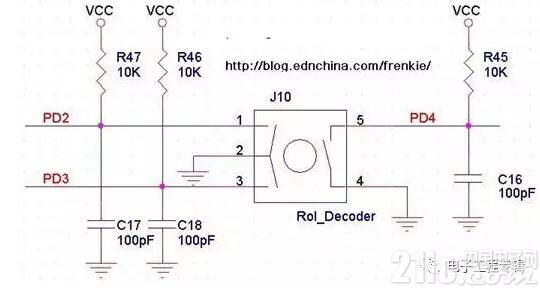

实际的电路

module quad(clk, quadA, quadB, count);

input clk, quadA, quadB;output [7:0] count;

reg [2:0] quadA_delayed, quadB_delayed;

always @(posedge clk) quadA_delayed <= {quadA_delayed[1:0], quadA};

always @(posedge clk) quadB_delayed <= {quadB_delayed[1:0], quadB};

wire count_enable = quadA_delayed[1] ^ quadA_delayed[2] ^ quadB_delayed[1] ^ quadB_delayed[2];

wire count_direction = quadA_delayed[1] ^ quadB_delayed[2];

reg [7:0] count;

always @(posedge clk)begin

if(count_enable)

begin

if(count_direction) count<=count+1; else count<=count-1;

end

end

endmodule

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码