什么是JESD209-6,为什么它对边缘AI很重要?

JESD209-6 是 JEDEC 最近发布的 LPDDR6(低功耗双倍数据速率 6)标准,代表了存储技术的重大飞跃,特别是对于功率预算有限的设备而言。它对于下一代移动设备、人工智能应用和边缘计算至关重要,在这些领域,高性能和能效至关重要。它还有望帮助限制数据中心应用的功耗。

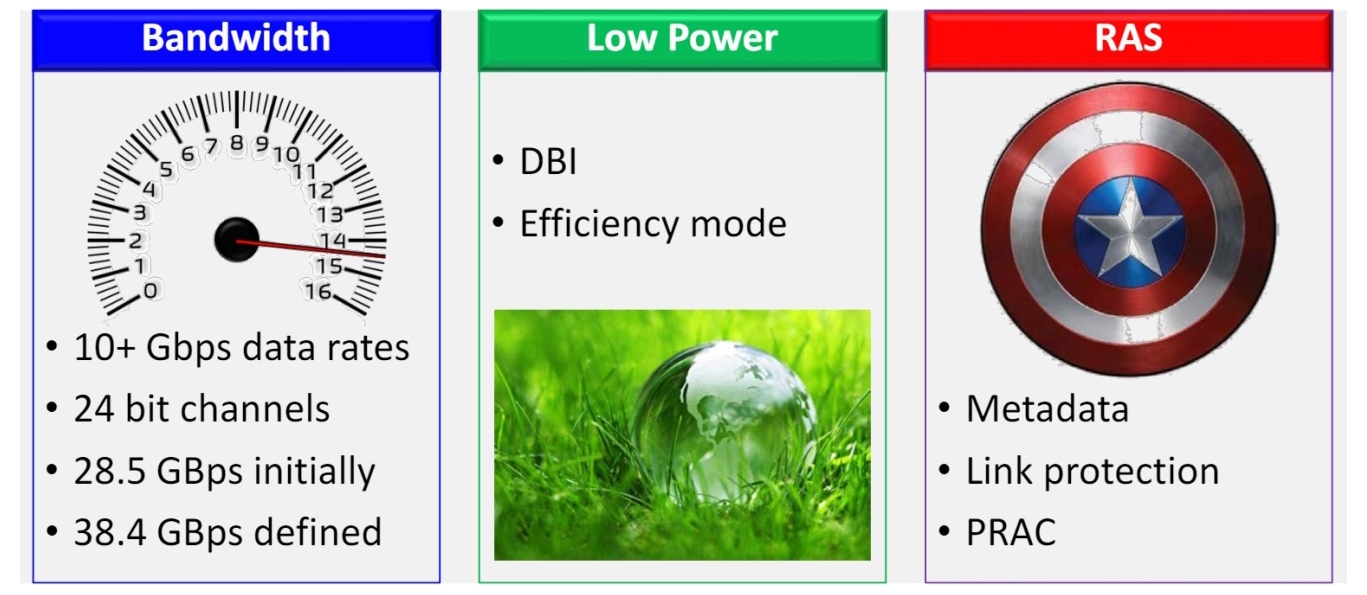

一些关键功能和改进包括增加带宽(路径高达 38.4 Gbps)、更低的能耗以及增强的可靠性、可用性和可维护性 (RAS)。

例如,数据总线反转 (DBI) 旨在提高内存作的性能和能效。每行激活计数 (PRAC) 通过监控和管理行激活来帮助维护 DRAM 数据完整性,防止潜在的数据损坏。(图 1)。

图 1.LPDDR6支持更高的带宽、更低的功耗和更高的可靠性。(图片来源:Tweak Town)

图 1.LPDDR6支持更高的带宽、更低的功耗和更高的可靠性。(图片来源:Tweak Town)

深入研究细节

架构和设计改进的结合使 LPDDR6 能够在 64 位总线上提供高达 38.4 GB/s 的最大带宽,是 LPDDR5 初始能力的两倍。LPDDR6 还提供了更大的灵活性,可实现更微调和性能优化。

双子通道架构支持每个子通道 12 条数据信号线 (DQ) 和 4 个专用命令/地址 (CA) 信号,从而实现更快的数据访问,并能够根据需求变化优化通道性能。

LPDDR6 中的信道宽度已从 LPDDR5 中的 16 位增加到 24 位。结合双子通道,更宽的通道进一步增强了整体内存带宽。这可能导致智能手机的带宽从 64 位增加到 96 位,笔记本电脑的带宽从 128 位增加到 192 位。

最后,LPDDR6 支持 32 字节和 64 字节突发之间的实时突发长度控制,有助于优化带宽和功耗。这对于处理可变 AI 工作负载的边缘设备尤为重要。

有几种降低功耗的新工具,包括 DBI 和添加第二个电源域。DBI支持功耗和降噪。

如果达到“0”位的预定阈值,则整个字节将反转,所有位从 0 翻转到 1,反之亦然。专用的 DBI 位用于指示数据已反转。反相旨在减少高到低转换的次数,从而降低开关噪声和功耗。

LPDDR6 还支持更复杂的电源管理,具有两种效率模式。静态效率模式专为持续的高吞吐量 AI 工作负载而设计。动态效率模式有助于优化低带宽场景(如处理传感器数据)的性能。

在动态效率模式下运行时,使用单个子通道。此外,LPDDR6 还增加了第二个电压域 VDD2,支持低活动期间的低功耗动态电压和频率缩放 (DVFSL)。

可靠性

当然,如果数据不可靠,高带宽和低功耗就没有用。LPDDR6 具有多项专门用于确保 RAS 的功能。PRAC 监控和管理行激活,帮助确保数据完整性。内存内置自检 (MBIST) 支持原位测试,有助于诊断和排除潜在问题。

LPDDR6 支持片上纠错码 (ECC),用于检测和纠正硬件级别的内存错误,支持命令/地址 (CA) 奇偶校验,用于检测命令和地址传输期间的错误。

如果检测到错误,错误清理功能有助于在存储单元中发生错误时纠正错误,以免它们累积并影响系统可靠性。分拆元模式支持为关键任务分配特定内存区域,隔离和保护重要数据和作。

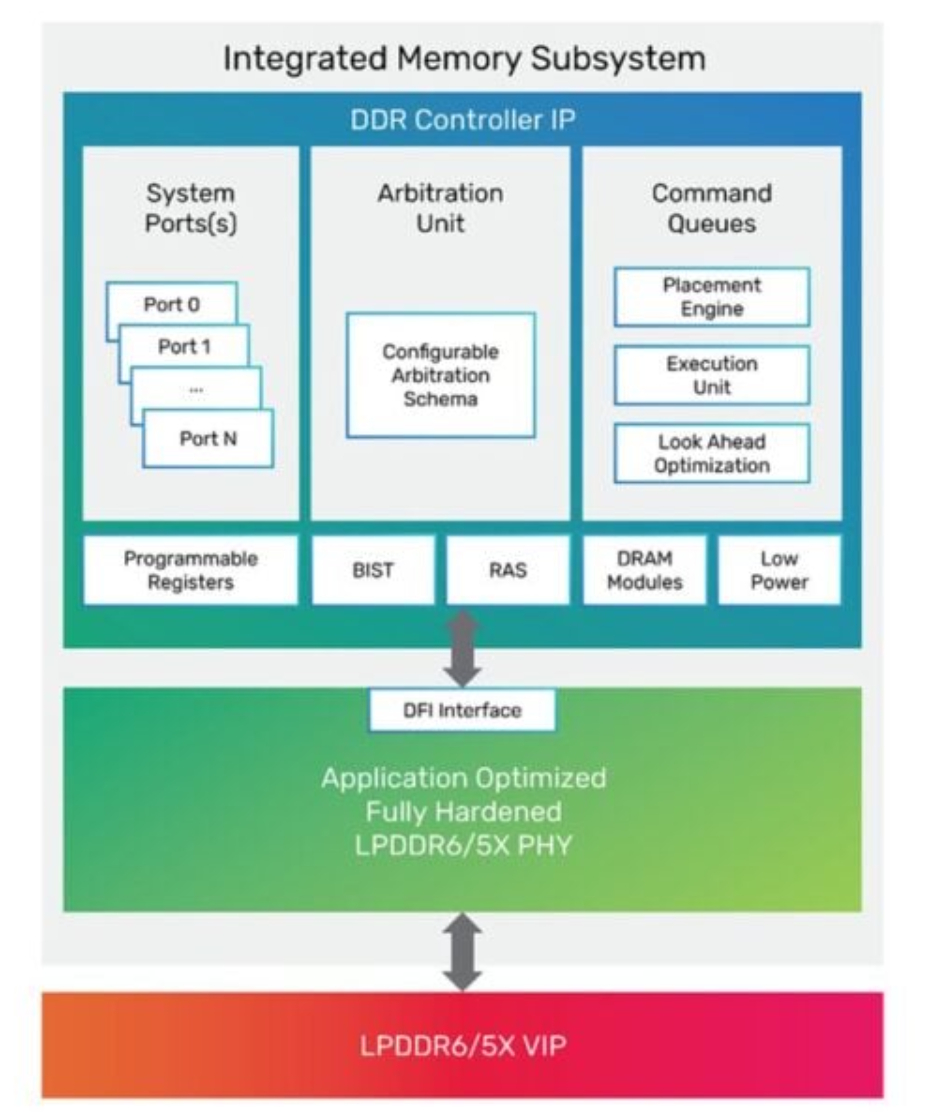

图 2.同时支持 LPDDR6 和 LPDDR5 的内存控制器 IP 框图,旨在最大限度地提高功耗、性能和面积 (PPA)。(图片来源:Cadence)

LPDDR6 内存控制器

LPDDR6 内存控制器已经上市。有些同时支持 LPDDR6 和 LPDDR5,以实现两代技术之间的平滑过渡。控制器支持原生集成到单片系统 (SoC) 和多芯片解决方案中。

支持高级内存接口,如 Arm AMBA AXI 总线。内存控制器以软寄存器传输电平 (RTL) 宏的形式作为可重用块提供(图 2)。

总结

JESD209-6,通常称为 LPDDR6,已针对在智能手机和笔记本电脑等功率有限的平台上运行 AI 应用程序进行了优化。与 LPDDR5 相比,它提供了更高的带宽、更低的能耗以及增强的可靠性、可用性和可维护性。最初的 LPDDR6 控制器 IP 也支持 LPDDR5,以简化向新技术的迁移。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码