功率电路进阶教程:固态断路器采用SiC JFET的四个理由

本教程聚焦SiC JFET 在固态断路器中的应用,核心内容包括三大板块,阐释 SiC JFET 的关键特性、系统说明 SiC JFET 如何推动电路保护系统取得重大进步、通过评估和测试结果展示产品性能。我们已介绍过浪涌电流、应对不断攀升的电力需求、为什么要使用固态断路器。本文为系列教程的第二部分,将介绍SSCB 采用 SiC JFET 的四个理由。

断路器制造商首要关注的是发热问题。 所有半导体在电流流过其中时都会产生热量。 这种热量可以用导通电阻来衡量, 其表示符号为 RDS(on) 。

当然, 制造商和工程师都希望 RDS(on) 尽可能小。 同时, 极低导通电阻这一特性也直接支撑着基于 JFET 的 SSCB 的另外三项优势:

▶ 尺寸极小

▶ 可靠性

▶ 易于使用

EMB 与许多其他断路器共用一个面板。 鉴于众多元件必须挤在断路器的局促空间中, 可用于散热的空间极为有限。 因此, EMB 制造商最关心的自然是发热问题。

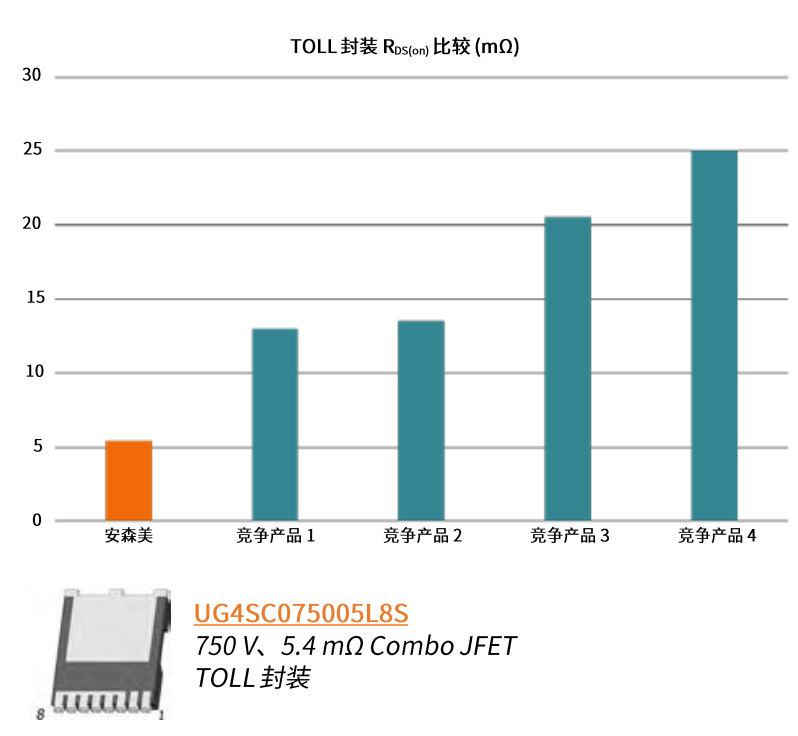

先进半导体设计对于解决这一问题至关重要 , 因为降低电阻可以直接减少热量的累积。 安森美(onsemi)的 JFET 和 Combo JFET TOLL 封装可使小型元件实现尽可能低的导通电阻 (RDS(on) )。

在下面的比较图中, 安森美 EliteSiC 封装的导通电阻不到相同 TOLL 封装的最接近竞争产品的一半。 此特性为固态断路器制造商带来了巨大的竞争优势。

极低的导通电阻

下图所示为未施加电压的安森美 SiC JFET 的横截面。 这里, 三个端子分别被标记为源极、 栅极和漏极。 有两个二极管, 每个二极管都有相应的电容:栅极和漂移区 PN 结处的漏栅二极管, 以及由 JFET 栅极偏置的栅源二极管。 每个沟道和栅极区构成一个单元, 单个 JFET 中存在数千个并联的单元。

注意漏极-栅极 PN 结周围的耗尽区。 由于缺乏移动载流子, 该区域呈现高电阻特性。 此时未施加电压, 该 JFET 处于未偏置状态。 在这种状态下, 耗尽区足够小, 允许电子沿着开放沟道的直接路径在源极和漏极端子之间自由流动 。 无PN 结或二极管挡在电流路径上, 且没有表面电流。 因此, 安森美 SiC JFET 被称为常开型。

这里的电流路径流经高导电性的 SiC 材料。 这使得 JFET 在给定电压额定值下具有极低的导通电阻。

将正电压 VDS 施加于漏极至源极时, 漏栅 PN 结反向偏置, 使耗尽区扩大。 如果 VDS 继续提高, 沟道会变得更狭窄。 最终耗尽区将填满沟道, 导致饱和。

安森美通过引入碳化硅材料 , 开发出一种专有晶圆减薄 方法 , 从而使EliteSiC JFET 尺寸更小、 发热更低。

在半导体晶圆制造过程中, 晶圆在薄膜沉积期间往往会发生一定程度的翘曲。 薄膜本身的内应力, 加上薄膜和衬底之间的热膨胀系数 (CTE) 不一致,使得一定程度的翘曲几乎难以避免 。 在减薄( 背面研磨) 过程中, 翘曲现象往往会加剧。

安森美开发了一种模拟晶圆上导致翘曲的内应力的方法 。 这使得工程师能够改进晶圆减薄工艺, 以尽量降低翘曲的影响。

常通型 JFET 的应用包括防雷保护、 限制浪涌电流、 取代 EMB 等。 然而, 大多数应用都要求断路器为常断型。

实现这种断路器的一种方法是将 SiC JFET 与低额定电压的常关型 Si MOSFET串联连接, 然后将 JFET 栅极连接至 MOSFET 源极。 在下图中, 对于变压器等开关模式应用所采用的标准共源共栅配置 , 连接通过直接短路实现。 如果 JFET栅极直接与 MOSFET 源极相连, 则开关速度至少比断路器和继电器所能承受的速度快 50 倍。 试图减慢如此高的开关速度是不切实际的。

另一种方法是引出 SiC JFET 的栅极, 然后与 Si MOSFET 串联连接。 这样一来,用户就可以选择 JFET 栅极和 MOSFET 源极之间的电阻或阻抗。 可以选用一个简单电阻或一个齐纳二极管, 使电流反向流动。

第二种方法可能是一种实用的解决方案, 特别是因为 JFET 和 MOSFET 元件成本非常低, 不过由于需要两个元件, 断路器将会占用更多空间 。 还有一种更好的解决方案。

安森美的解决方案是堆叠芯片。 EliteSiC Combo JFET 将常开型 SiC JFET 与常关型 Si MOSFET 串联连接。 但是, JFET 栅极和 MOSFET 栅极均被引出到封装外部,而不是将栅极连接到封装内部的源极 。 这使得用户能够以适合应用的任何方式连接封装。

如下图所示 , 蓝色 SiC JFET 芯片通过银焊与封装的铜底座中心连接 。 黄色 Si MOSFET 芯片居中置于 JFET 芯片的上方。 每个芯片的栅极均通过单独的引脚分别引出。

减少空间消耗的另一种方法是尽量减少并联使用的元件数量。假设要制作一个 240 V 交流断路器, 其额定电流为 20 A, 能够承受 1.2 倍过载 2小时。 应用经典焦耳加热公式 P = i2R 来计算功率耗散, 总热量预算可表示如下:

同样, 关键因素是所需的RDS(on)。 假设工作温度保持在 100 °C, 导通电阻自然会随着温度成比例增加。将等式两边除以电流的平方, 即可得出所需的导通电阻:

为了满足导通电阻目标并使导通损耗加倍, 两个 Combo JFET 需要背靠背或串联连接, 源极并联连接。 Combo JFET 数量加倍会使断路器中用于阻断电流的内部元件数量达到 4 个( Combo JFET 算作两个元件) 。

如果选择竞争对手提供的同类 TOLL 封装元件, 要满足导通电阻要求, 元件数量最低的方案也需要 5 个并联 JFET ( 其在 100 °C 时的额定电阻为 21 mΩ) ,总计 10 个元件。

片上温度感测: JFET 或 Combo JFET

SiC JFET 有一个常被忽视的优点, 即它能够感知自身的温度。 当栅极被驱动为略正( “ 过驱” ) 时, 会注入一个非常小( 1 - 5 mA 范围) 、 绝对安全的电流。 这个小电流使得 VGS为正, 并以高度可预测的方式随温度变化。 通过测量 VGS 的压降,便可使用公式推导出 JFET 芯片的温度。

上面的温度感测驱动电路示意图包含两个差分放大器 ( diff -amp ) , 每个放大器测量 JFET 至 MOSFET 源极电压。 SiC JFET 和 Si MOSFET 均采用串联复制, 并以背靠背方式镜像排列, 用于阻断交流电流。 单个基准电压连接到共源点, 差分放大器从该电压中减去各自的 VGS。 当电流接通时 , 电流从 AC 1 流向 AC 2, 使得每个MOSFET 两端出现压降。

为了得出芯片温度,需要测量从每个 JFET 的栅极到其共源点的电压。两个差分放大器的输出表示为:

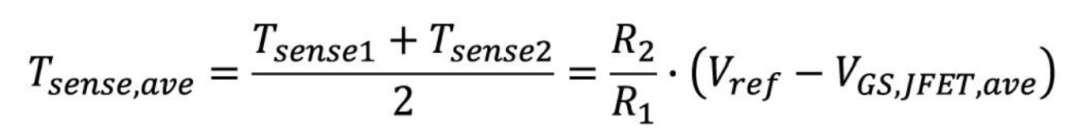

较为准确的温度读数是取 Tsense 1 和 Tsense 2 的平均值, 即将这两个值相加再除以 2。

成对使用的差分放大器常用于对噪声进行等量反相放大 , 使正负噪声叠加后相互抵消 。 这里, 我们正是利用了这一技术 ,通过成对的差分放大器, 使两个压降值 |VDS,MOSFET |相互抵消。 剩下的是一个简化公式, 其中温度等于增益乘以基准电压与两个 JFET 的平均栅源电压之差。

仅需约 1 mA 的栅极电流就足以降低导通电阻。 虽然用如此低的栅极电流来感测温度确实可行, 但 5 - 10 mA 范围内的电流更不容易受到噪声的影响。

同样精巧的技术也可应用于 JFET 或 Combo JFET 来测量电流。 该方法需要两个相同的二极管 D1 和 D2, 它们与 Combo JFET 的漏极串联连接, 能够阻断高电压。 将栅极驱动器与 DESAT ( 去饱和) 引脚结合使用时, 可通过这两个二极管提供 mA 至 μA范围的小电流。 或者, 也可从栅极驱动电源通过一个电阻提供小电流。

无论哪种情况, 都需要箝位二极管 D1, 并在其上使用一个放大器 , 以测量该二极管两端的电压降 。 此压降代表 JFET 的 VDS。 知道芯片温度便可轻松估算RDS(on) , 进而可利用欧姆定律来估算漏极电流, 而无需使用额外的传感器:

知道芯片温度和漏极电流后, 就能开发出对过流状况立即做出响应的温度补偿器。 Combo JFET 的导通电阻 RDS(on) 随温度升高而增加, 表现出正温度系数特性。 在给定电流下, 随着温度升高, VDS 提高, VGS降低。

将这两个值合并后输入快速过流模拟比较器 , 便可使这两个电压相互抵消 ,从而消除温度影响。比较器将 VDS 与动作电压进行比较, 从而实现有效的温度补偿。 受限于 RDS(on)与 Tsense,ave之间的非线性关系, 补偿效果略有减弱。 然而, 在典型工作温度范围内, 这种补偿完全足够, 因此无需使用微控制器或状态机以数字方式进行温度补偿调整。可能需要额外的电路来应对 JFET 关断和重新导通方面的问题, 包括处理消隐时间和复位比较器的输入电压。碳化硅 JFET 天然具备高脉冲电流能力 。 下图展示了未箝位感性开关设置的开关导通事件, 其中电源电压由电缆电感供应给 Combo JFET 中使用的相同 4.3 mΩ JFET 。 其峰值脉冲电流 IDM 额定值为 588 A, 该图显示其在 600 A 时切换, 斜坡时间约为 24 ms 。 电感中储存的能量部分被 JFET 吸收, 其余由并联的金属氧化物压敏电阻箝位。 漏源电压 VDS 在被箝位之前上升至接近 600 V。 这证明 SiC JFET 具有高峰值电流能力。 这是一个很大的优势, 尤其是在断路器应用中, 因为在这类应用中, 不可避免地需要切换非常高的峰值电流( 远高于标称电流)。

考虑断路器时, 无论是固态断路器还是机电式断路器, 电压裕度都是最重要的考量因素之一。 这与电压额定值不同。 住宅和轻型商业应用的通用输入电压范围为 85 至 265 VAC, 峰值电压为该范围的最大值乘以 √2, 即 375 VAC。

电压额定值为 400 VAC 的断路器无法提供所需的电压裕度。 原因是从供电端到用电设备接线点的电缆中, 以及从用电设备接线点到断路器的电线中 , 都会储存能量。当发生涉及非常高电流的故障情况时 , 通向断路器的电缆和电线中储存的能量可能非常高。 如果电流断路器在此类情况下关断 , 那么所有这些能量必须转移到某个地方。

使用 SiC JFET 时, 需要将尽可能多的这种电流转储到该芯片中。 但它本身只能处理有限的能量, 肯定无法处理电缆和电线中储存的所有能量 。 为了处理额外的能量, 需要添加并联金属氧化物压敏电阻 (MOV) 或瞬态电压抑制器(TVS) 。

根据安森美的经验, MOV 的特性曲线比该图所示更加圆润, 意味着它通常需要更多时间才能激活。 当峰值电流较高时, MOV 两端也会出现相应的高电压。 SSCB 中使用的 JFET 必须具有足够高的电压额定值, 以确保当电压处于正常工作范围时, MOV 的漏电流不会过大。

根据 Creative Commons 4.0 授权使用

这不仅提高了其可靠性, 而且使其更容易在采用低成本箝位器件( 如 TVS 或 MOV)的断路器设计中使用 。 在过载条件下 , 尤其是在电压过冲情况下 ( 即在电源转换事件期间, 输出电压超过预期的稳态电压设置值 ) , 这种高电压额定值可提供更高的安全裕度。

如右侧的电路图所示, 只需使用低成本的现成元件, 便可轻松驱动 SSCB 中使用的Combo JFET 封装中的 JFET 和 MOSFET 。 该电路显示两个 Combo JFET 背靠背连接, 其源极连接在一起, 并有一个共源点。 以这种方式连接时, 这两个元件可以阻断交流电流。

通过这种设计, 可以使用一个 IGBT 直接驱动两个 Combo JFET 的栅极, 提供电压和电流去饱和保护。 当该电路接通时, 过驱电阻 R_ODV 便开始发挥作用, 限制流入每个 JFET 栅极的电流。 开关导通速度可能很慢, 不过这对于断路器来说可能是一个优点。 接下来, JFET 基于其温度来设置自己的 VGS。

设置关断状态是通过调整 JFET 栅极电阻实现的。 这种方式可提供出色的速度控制, 因为所有输出电容电荷都经过该电阻。

MOSFET 可以由如图所示的电压监控器驱动 , 或者由单独的栅极驱动器驱动 。一旦栅极驱动功率逐渐上升 , MOSFET 就会导通并保持导通状态。 由于保持导通状态, MOSFET 不会受到压力, 发生雪崩的可能性也不会增加 。 此后, 开关操作由 JFET 的导通和关断来控制, 开关速度则通过调整栅极电阻来控制。 所有开关能量都进入 SiC JFET , 这正是我们所希望的。

通过这种设计 , 电路可以在紧急情况下接通和关断 , 就像在正常运行情况下接通和关断一样。 还可以通过脉冲控制电路, 以限制电容充电时的浪涌电流。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码