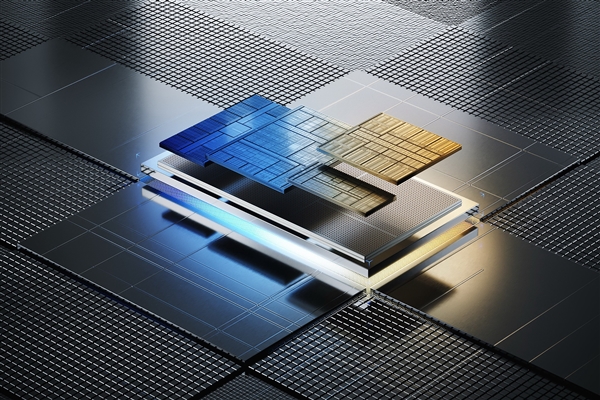

硅通孔(TSV)复杂度引发制造瓶颈

制作硅通孔是必要但极具挑战的难题。

硅通孔(TSV)为高带宽内存堆栈中的 DRAM 裸片、硅中介层以及新兴 3D 芯片堆栈提供关键互联。但随着 TSV 尺寸不断微缩,其制造成本急剧上升,且更容易出现缺陷。

TSV 是集成 MEMS、射频、模拟 IC、GPU 等芯片的必备技术。它能提升单裸片性能,作为高频电信号的垂直传输线,优化多裸片系统表现。但随着器件密度提升,TSV 密度也随之增加,进而要求通孔间距更小、TSV 尺寸与微凸点更小。这会引发信号完整性问题,需要全新屏蔽方案,并加速向混合键合过渡。

目前,全球仅有少数企业具备先进封装与组装能力。AI 热潮导致 HBM(及其他主流存储)缺货,可生产搭载 TSV 的 2.5D/3D 系统的先进封装产能,远跟不上需求爆发式增长。

TSV 可在制造流程的先、中、后三个阶段制作,这通常决定了由谁整合工艺。例如,日月光、安靠等 OSAT 厂商通常采用TSV 后制程(露孔工艺);台积电、三星等晶圆厂则采用TSV 先制程与中制程;英特尔代工服务则在中介层与嵌入式芯片平台均支持 TSV 集成。

TSV 的尺寸跨度极大:

2nm 及以下工艺使用nanoTSV(<100nm),为晶体管供电轨提供更高效供电。

硅中介层中的 TSV 直径可达5–20μm,深度80–120μm,贯穿减薄后的硅片,通过焊球连接上方芯片或下方 PCB。

TSV 对机械应力敏感,需要设置禁布区(keep-out zones) 限制通孔间距。高深宽比结构易产生空洞、接缝等缺陷,需要优化刻蚀与电镀工艺以保证良率与长期可靠性。

下文将解析 TSV 制造为何如此困难,以及如何降低成本。

TSV:特殊的铜互联

TSV 技术起源于约 20 年前,东芝率先将其用于 CMOS 图像传感器,尔必达将其用于手机 DRAM。相比传统引线键合与倒装凸点,TSV 连接更优,且属于芯片级封装延伸,不会增大封装体积。

TSV 逐步应用于 CMOS 图像传感器、FPGA、HBM 堆栈、传感器、MEMS / 逻辑、射频模块、缓存 / 处理器堆栈,并即将用于光子 IC 与电子 IC 互联。

HBM 是最受关注的 TSV 应用场景,美光、SK 海力士、三星均在内部完成 TSV 制程。HBM 内部 TSV 直径通常2–5μm,深度30–60μm,采用TSV 中制程(前道器件后制作通孔),在密度、成本、热约束间取得最佳平衡。TSV 呈规则阵列排布,避开模拟与高应力区域。

硅中介层同时通过 TSV 实现垂直连接,通过重布线层(RDL)实现水平连接。其中 TSV 尺寸大于 HBM,直径5–20μm、深度80–120μm,成簇分布在微凸点阵列下方、布线通道、裸片边缘与供电区域。晶圆厂负责硅中介层制造,少数专业厂商提供中介层服务,但具备先进能力的极少。AI 扩张带来的压力正冲击整条供应链,并将推动未来变革。

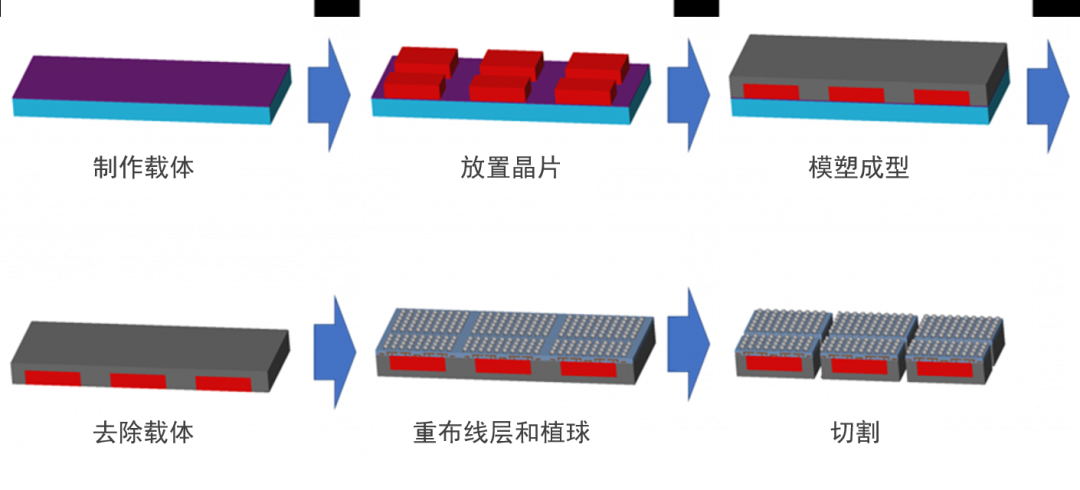

TSV 制造流程

TSV 制造每一步都至关重要,其中几项挑战尤为突出:

刻蚀:尺寸微缩使深孔底部残留物更难清除,同时要保持近乎垂直的轮廓。轮廓决定氧化衬层、阻挡层、铜种子层的附着与共形性,顶部收口会形成空洞,威胁可靠性。

铜电镀:理想为自下而上填充,需要精准控制药液。

化学机械抛光(CMP):去除顶部多余铜。

TSV 露孔:最关键的最后一步。晶圆临时键合在载体上后,经粗磨、中磨、精磨,再用 CMP 接近通孔,最终通过等离子刻蚀露出 TSV。

安靠高级 3D 产品总监里克・里德表示:干法刻蚀对硅片损伤小,晶圆在刻蚀前已打磨至镜面,保障表面质量。

精准的 TSV 露孔流程包括:

标定博世刻蚀形成的 TSV 深度

均匀涂布键合胶与解离层,烘烤固化后键合

背面减薄至 TSV 底部数微米内

多阶段 CMP

等离子刻蚀露出 TSV

沉积氮化硅抛光停止层

沉积厚二氧化硅

CMP 至 TSV 露出

露孔后,TSV 仍由氧化衬层保护,避免金属接触空气。随后沉积氮化硅钝化,再覆盖厚氧化层,经 CMP 后露出与钝化层共平面的铜 TSV,形成可加工的平坦表面。

晶圆减薄优化中,临时键合材料选择至关重要,需考虑热预算、解离方式、与薄膜兼容性。前沿技术倾向机械与激光解离。

减薄的关键指标是总厚度变化(TTV),低于 5% 对堆叠与阵列至关重要,超标会导致键合不均、黏附失效或分层。

详细制程步骤

图形化与刻蚀圆柱形深孔

博世深反应离子刻蚀(DRIE)形成各向异性沟槽

PECVD 沉积氧化硅衬层,防止铜污染硅片

PVD/ALD 沉积 TaN/TiN 阻挡层

沉积铜种子层

电化学沉积(ECD)铜,无空洞填充

CMP 抛平顶部多余铜

沉积焊球或重布线层

缺陷防控

高宽比(>10:1)TSV 易出现两类缺陷:

TSV 顶部损伤

侧壁条纹

这会降低金属填充质量与电学性能。泛林研究表明,缩短预涂层时间、降低偏压可消除顶部损伤;低压、高压强可抑制侧壁条纹。

电镀后铜空洞会导致电阻升高、机械强度下降甚至失效。其他常见缺陷:图形对准偏差、沉积不均、填充不完整,均影响性能与可靠性。

边缘缺陷是晶圆减薄最受关注的问题,微小缺陷即可导致晶圆断裂。

应力管理

硅(2.8 ppm/°C)与铜(17 ppm/°C)热膨胀系数失配会产生机械应力。工程师通过仿真建模、拉曼光谱、X 射线衍射、有限元分析(FEA)评估应力分布,设置禁布区避免影响有源器件。

设计软件需集成应力与热仿真,多芯片模块需经过严格应力与疲劳测试。

纳米 TSV(nanoTSV)

三大晶圆厂(英特尔、台积电、三星)正为 2nm 及以下工艺研发背面供电架构,将供电与信号线分离,可降低30% 功耗,减少电压跌落与 RC 延迟,释放正面布线资源,节省光刻成本。

背面供电有三种技术路线,复杂度逐级提升:

最激进:器件制作前在环绕栅极间制作 nanoTSV

中等:电源通孔连接背面供电网络与正面接触层

最保守:供电线跨已制成器件

最大挑战是背面与正面图形互联的套准精度。比利时微电子研究中心(Imec)提出自对准狭缝 nanoTSV 方案,实现约 100nm 套准裕度,可避免高阶光刻校正,降低成本。

结论

HBM 厂商、头部晶圆厂与 OSAT 均在芯片与模组生产的不同阶段提供 TSV 制造能力。随着 HBM 中 DRAM 晶圆持续减薄,需要更多、更小的 TSV 支撑存储单元增长。

硅中介层 TSV 布局更灵活,以连接为目标,可加入虚拟 TSV 平衡应力。

nanoTSV 则为背面供电提供前后侧关键互联。

无论尺寸与应用如何,TSV 将长期存在,工程师正持续探索更具成本效益的制造方案。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码